# A Theoretical Framework for Symbolic Quick Error Detection

FLORIAN LONSING SUBHASISH MITRA CLARK BARRETT

Paper published at Formal Methods in Computer-Aided Design (FMCAD) 2020 Preprint: <a href="https://arxiv.org/abs/2006.05449">https://arxiv.org/abs/2006.05449</a>

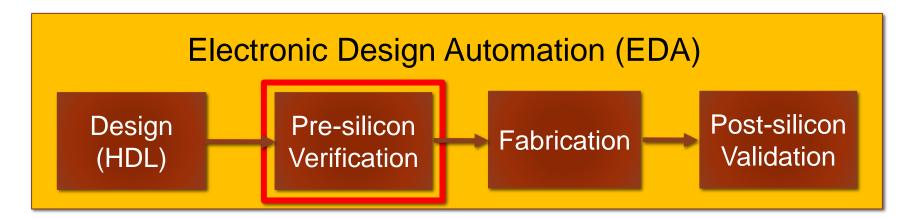

#### Context: Pre-Silicon Verification

- Our focus: processor designs.

- Formally verify model of a design (e.g. Verilog).

- Model checking vs. non-formal simulation or testing.

#### Context: Pre-Silicon Verification

- Our focus: processor designs.

- Formally verify model of a design (e.g. Verilog).

- Model checking vs. non-formal simulation or testing.

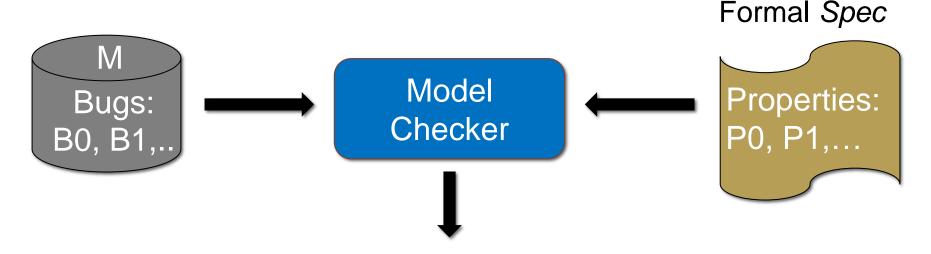

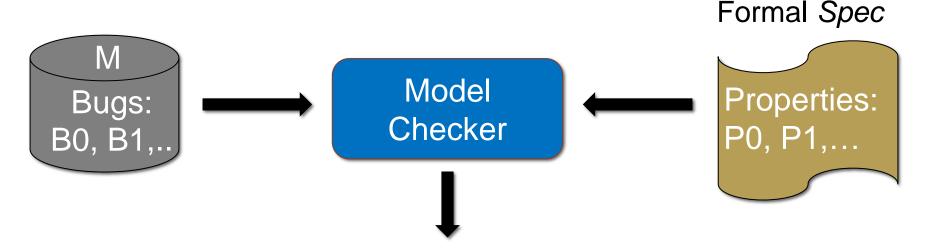

## Soundness of Bug-Finding

Does  $P \in Spec$  hold in M?

- If  $P \in Spec$  fails then  $B \in M$ .

- Property P covers bug B.

Soundness ≈ no spurious cex

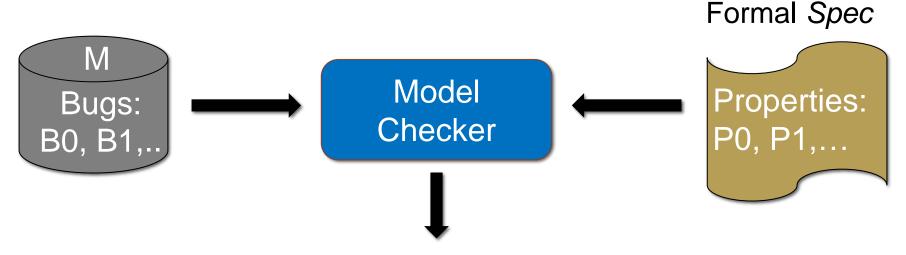

Does  $P \in Spec$  hold in M?

- If  $B \in M$  then  $P \in Spec$  fails.

- Property P covers bug B.

Completeness ≈ Spec covers all bugs

• "Have I written enough properties?" [Katz et al. CHARME'99].

Does  $P \in Spec$  hold in M?

Challenge: making Spec complete.

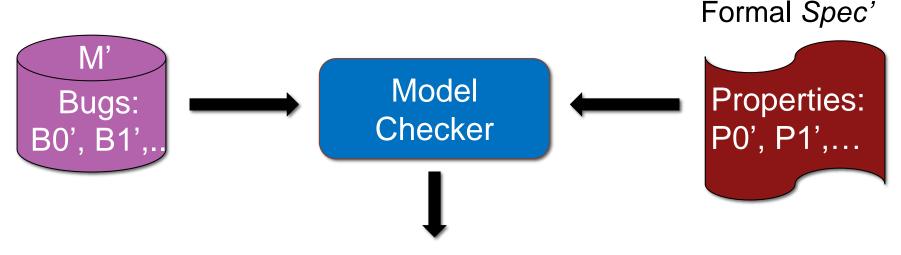

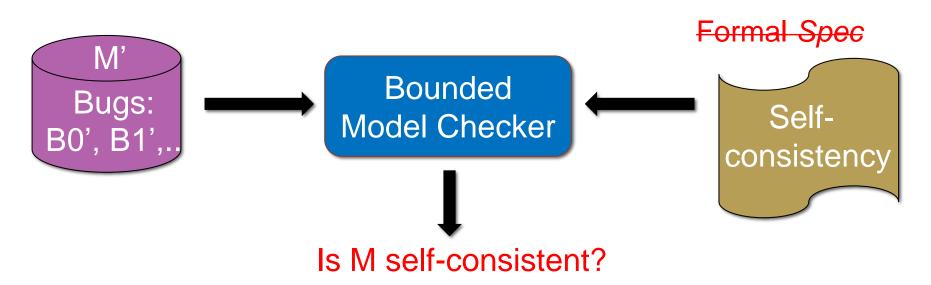

Does  $P \in Spec$  hold in M?

Spec: manual writing of implementation-specific properties.

Does  $P \in Spec'$  hold in M'?

- Spec: manual writing of implementation-specific properties.

- Model/design changes → Spec to be adapted (manually).

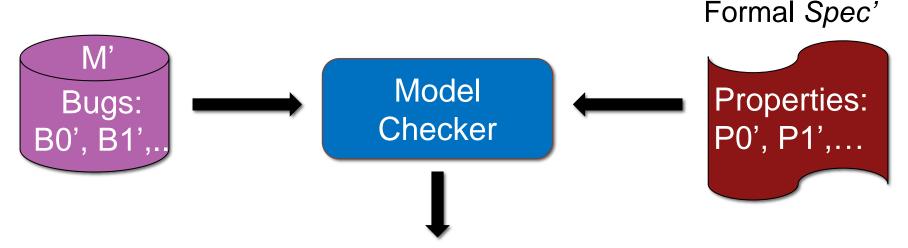

Does  $P \in Spec'$  hold in M'?

- Spec: manual writing of implementation-specific properties.

- Model/design changes → Spec to be adapted (manually).

- Completeness depending on Spec.

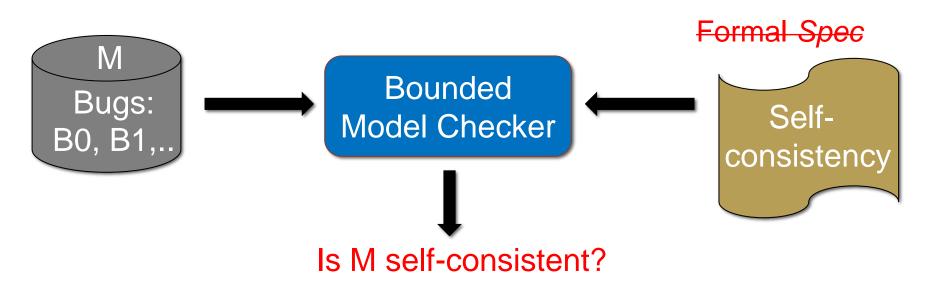

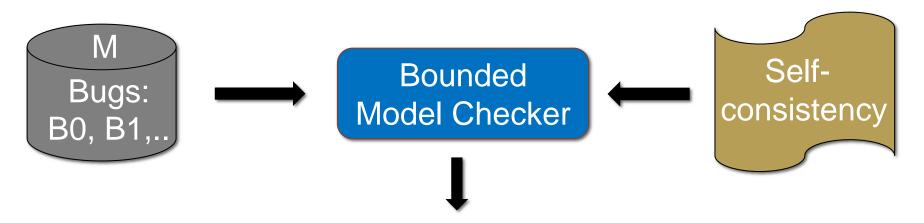

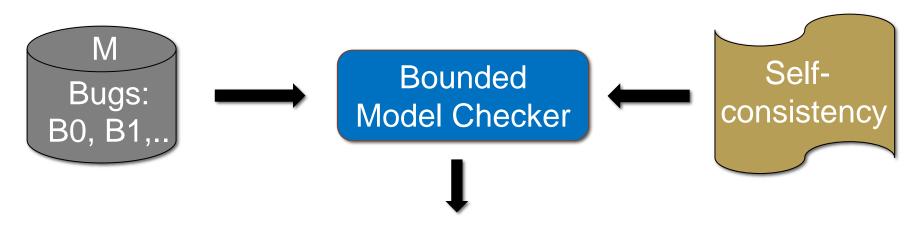

## Symbolic Quick Error Detection (SQED)

- No need for Spec or implementation-specific properties.

- Leverages bounded model checking (BMC).

## Symbolic Quick Error Detection (SQED)

- No need for Spec or implementation-specific properties.

- Leverages bounded model checking (BMC).

- Self-consistency: universal property, no manual writing.

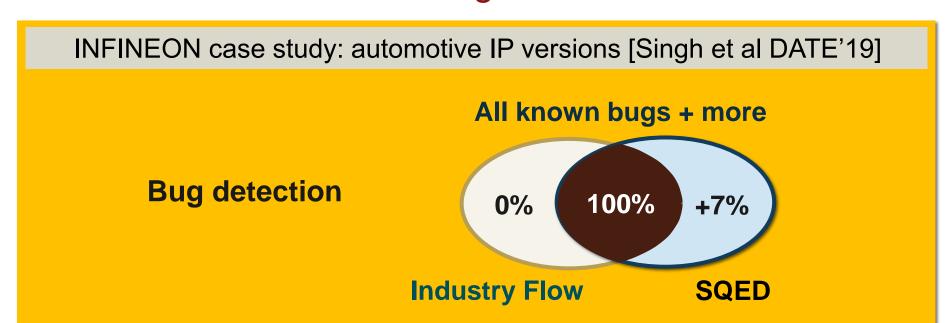

## SQED: Industrial Strength

#### **Traditional verification:**

(Constrained) random simulation, directed tests, formal.

#### Our Contributions: SQED Formal Proofs

Does  $P \in Spec$  hold in M?  $\approx$  Is M self-consistent?

- 1. Soundness: no spurious cex.

- 2. (Conditional) completeness: all bugs covered (BMC depth).

- 3. Formal framework: abstract processor model.

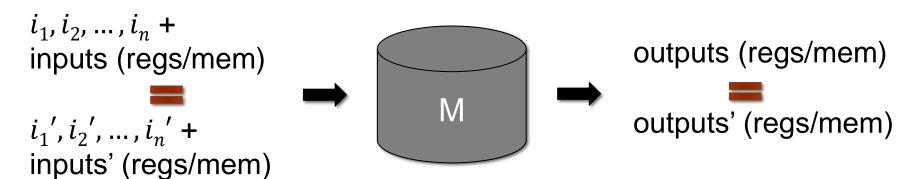

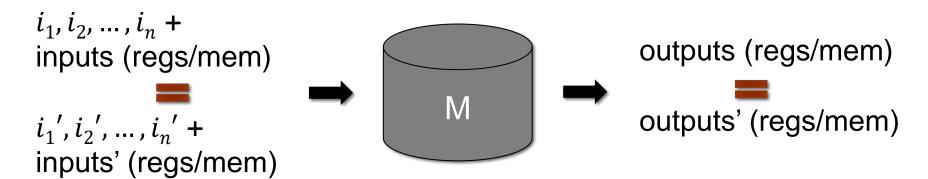

## Self-Consistency

- Function f: equivalent inputs → equivalent outputs.

- Functional congruence property:

$$\forall x, x' : x = x' \rightarrow f(x) = f(x')$$

## Self-Consistency

Processor Design M:

## **Self-Consistency**

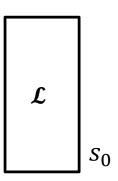

Processor Design M:

HW designs have complex internal state (pipeline,...).

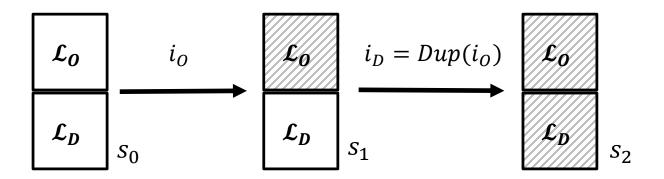

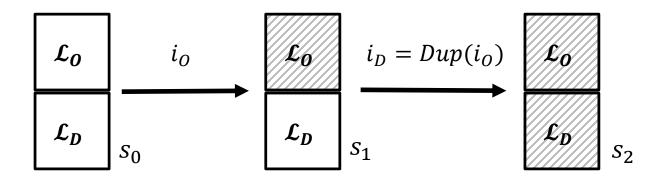

- State  $s_0$ : mapping from locations  $\mathcal{L}$  to values.

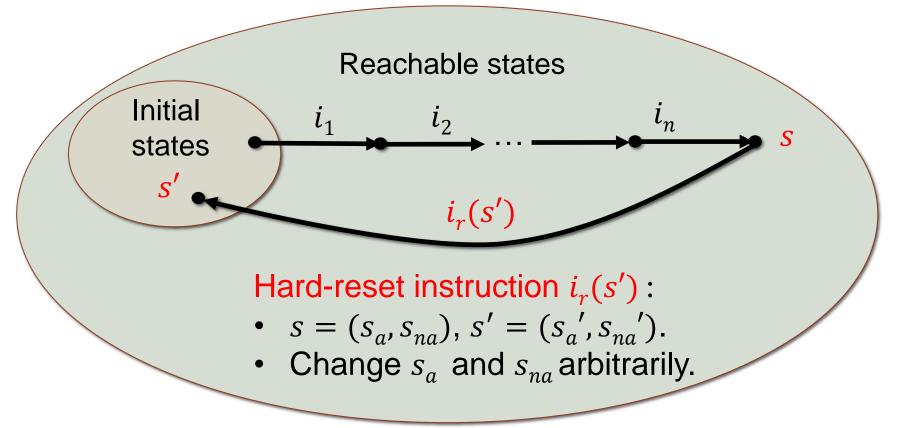

- (Non-)architectural parts of  $s_0 = (s_a, s_{na})$ .

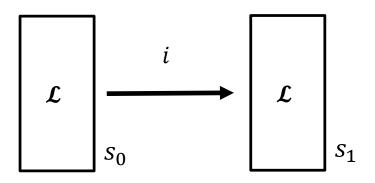

- $\mathcal{L}$ : regs. and mem. locations, value  $s_0(l) = s_a(l) = v$ .

- Instruction i = (op, l, (l', l'')), one-step execution.

- Opcode op, input locations (l', l''), output location l.

- Transition:  $T(s_0, i) = s_1, s_0 = (s_a, s_{na}), s_1 = (s_a', s_{na}').$

Example: register identifiers

$$\mathcal{L} = \{0, 1, ..., 31\}$$

$\mathcal{L}_{0} = \{0, ..., 15\}$

$\mathcal{L}_{D} = \{16, ..., 31\}$

$L_{D}(l) = l + 16$

- Partition of  $\mathcal{L}$ : original and duplicate locations  $\mathcal{L}_0$ ,  $\mathcal{L}_D$ .

- Arbitrary, fixed bijective mapping  $L_D: \mathcal{L}_O \to \mathcal{L}_D$ .

- Self-consistency property based on mapping L<sub>D</sub>.

#### Example:

$$i_0 = (ADD, l_{12}, (l_4, l_8))$$

$L_D(l) = l + 16$

$i_D = (ADD, l_{28}, (l_{20}, l_{24}))$

- Original instruction  $i_0 = (op, l, (l', l''))$ .

- Duplicate  $i_D = Dup(i_O) = (op, L_D(l), L_D(l', l''))$ .

- Original instruction  $i_0 = (op, l, (l', l''))$ .

- Duplicate  $i_D = Dup(i_O) = (op, L_D(l), L_D(l', l''))$ .

- Original/duplicate  $i_O/i_D$  operates on  $\mathcal{L}_O/\mathcal{L}_D$  only.

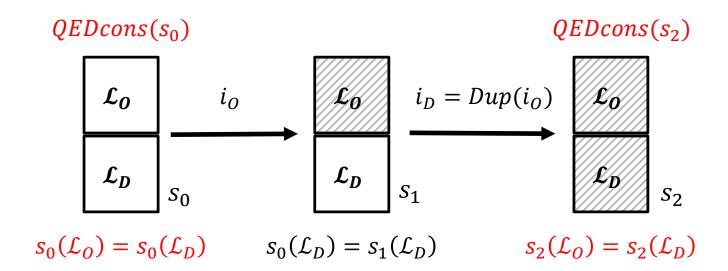

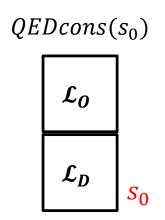

- Given  $L_D$ , state  $s_0$  QED-consistent  $\leftrightarrow s_0(\mathcal{L}_D) = s_0(\mathcal{L}_D)$ .

- Matching values at original/duplicate locations.

- Given  $L_D$ , state  $s_0$  QED-consistent  $\leftrightarrow s_0(\mathcal{L}_D) = s_0(\mathcal{L}_D)$ .

- Matching values at original/duplicate locations.

- Correct execution of  $i_O/i_D$  preserves QED-consistency.

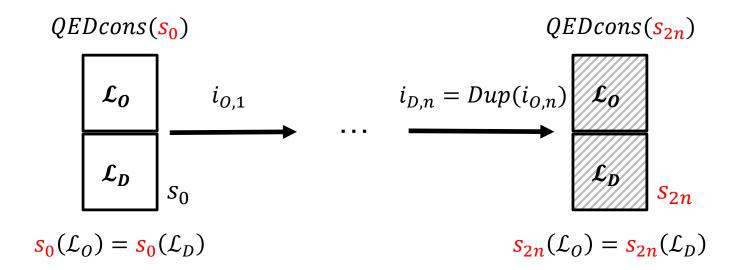

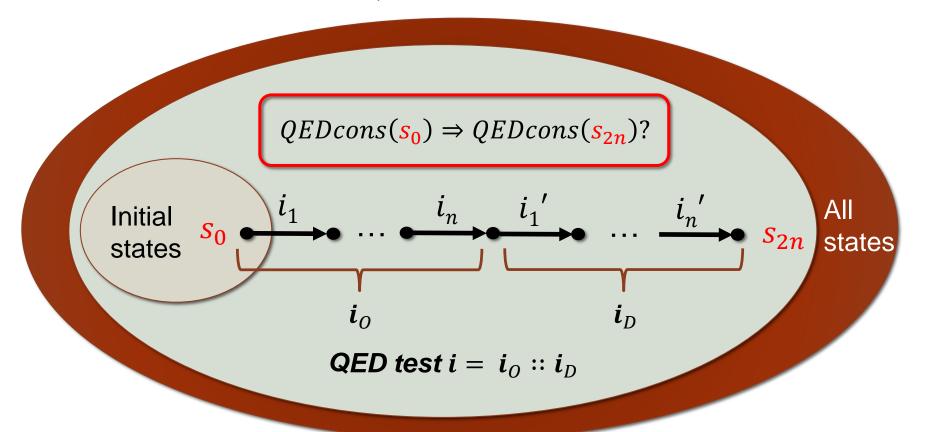

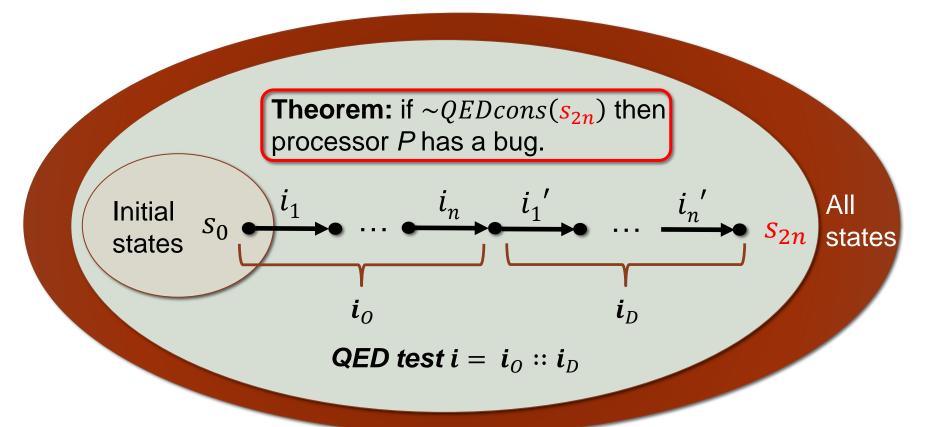

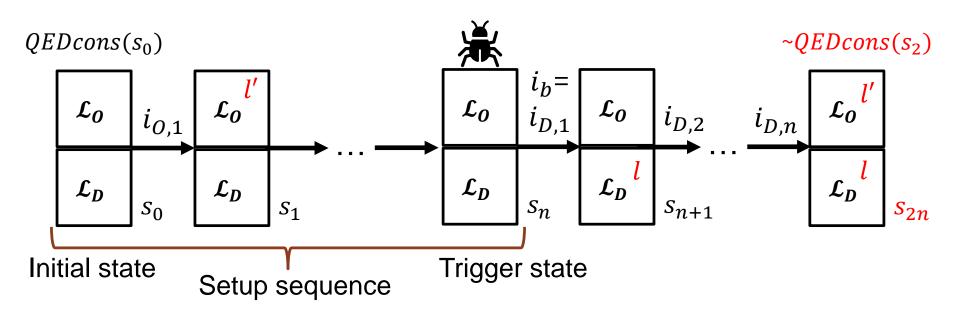

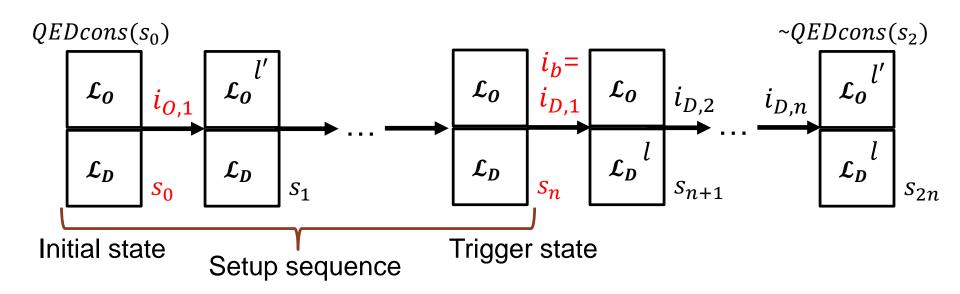

- $i_O = i_{O,1}, ..., i_{O,n}$  and  $i_D = i_{D,1}, ..., i_{D,n}$  with  $i_D = Dup(i_O)$ .

- QED test: concatenation  $i = i_0 :: i_D$  of 2n instructions.

- Correct execution of i preserves QED-consistency.

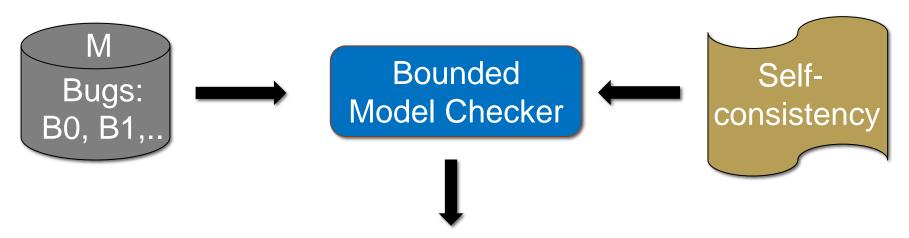

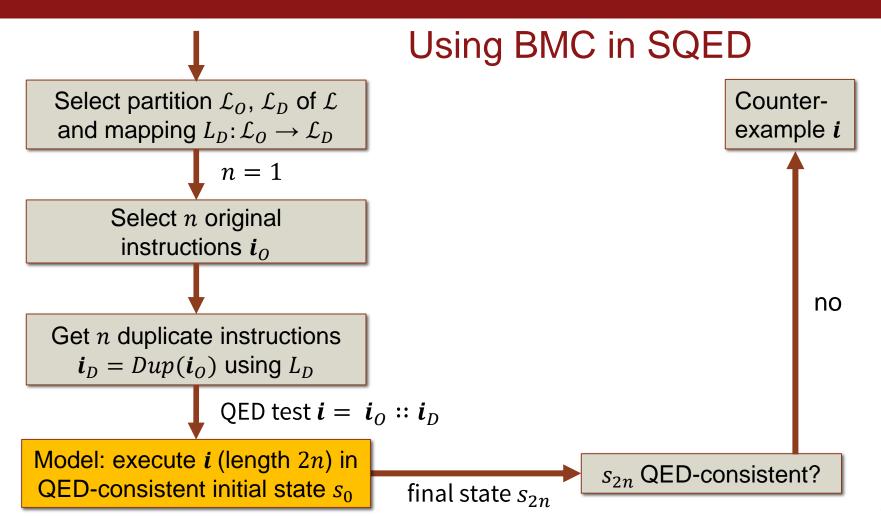

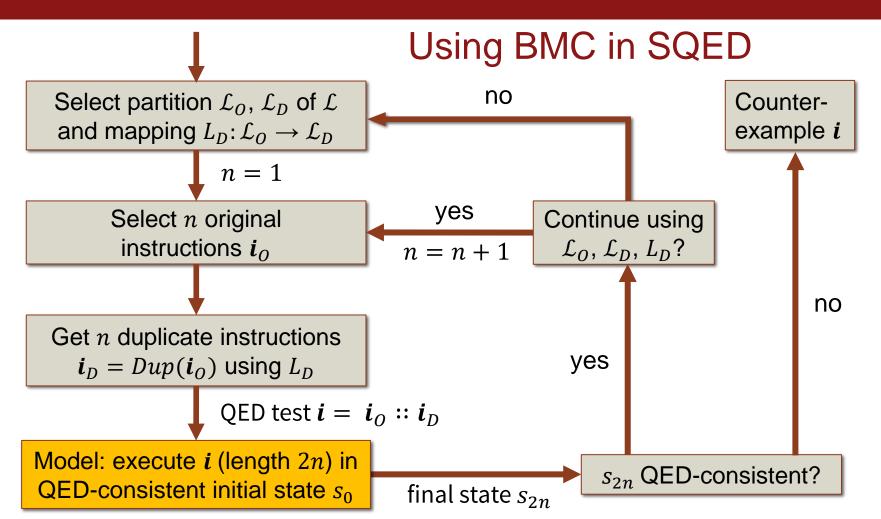

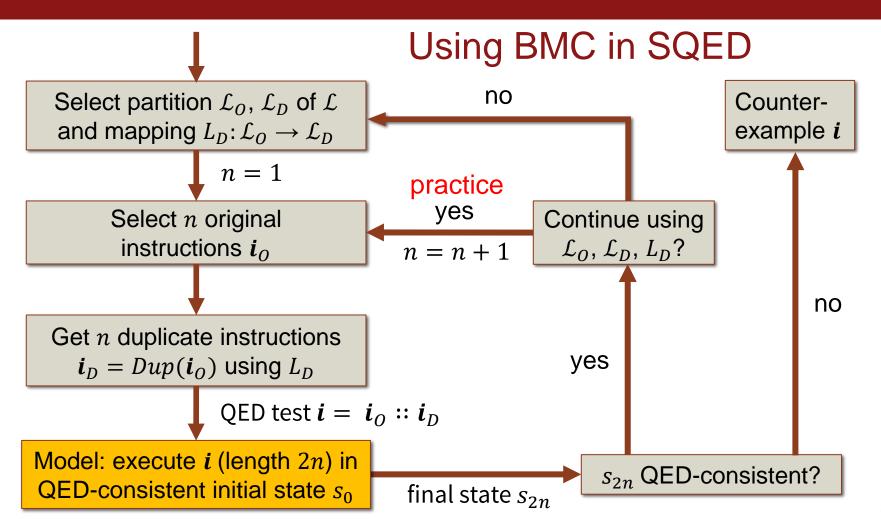

## Using BMC in SQED

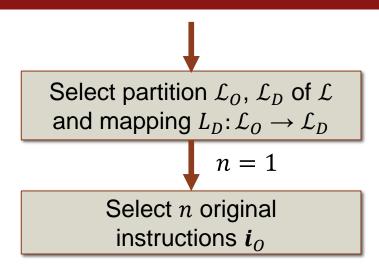

Select partition  $\mathcal{L}_{O}$ ,  $\mathcal{L}_{D}$  of  $\mathcal{L}$  and mapping  $\mathcal{L}_{D}$ :  $\mathcal{L}_{O} \to \mathcal{L}_{D}$

## Using BMC in SQED

## Select partition $\mathcal{L}_{O}$ , $\mathcal{L}_{D}$ of $\mathcal{L}$ and mapping $L_D: \mathcal{L}_O \to \mathcal{L}_D$ n = 1Select *n* original instructions $i_0$ Get *n* duplicate instructions $i_D = Dup(i_O)$ using $L_D$

## Using BMC in SQED

## Using BMC in SQED

Select partition  $\mathcal{L}_{O}$ ,  $\mathcal{L}_{D}$  of  $\mathcal{L}$  and mapping  $L_{D}$ :  $\mathcal{L}_{O} \to \mathcal{L}_{D}$

$$n = 1$$

Select n original instructions  $i_0$

Get n duplicate instructions  $i_D = Dup(i_O)$  using  $L_D$

QED test

$$i = i_0 :: i_D$$

Model: execute i (length 2n) in QED-consistent initial state  $s_0$

## Using BMC in SQED

Select partition  $\mathcal{L}_{O}$ ,  $\mathcal{L}_{D}$  of  $\mathcal{L}$  and mapping  $L_{D} \colon \mathcal{L}_{O} \to \mathcal{L}_{D}$

$$n = 1$$

Select n original instructions  $i_0$

Get n duplicate instructions  $i_D = Dup(i_O)$  using  $L_D$

QED test

$$i = i_0 :: i_D$$

Model: execute i (length 2n) in QED-consistent initial state  $s_0$

final state  $s_{2n}$

$s_{2n}$  QED-consistent?

## **Abstract Specification Relation**

```

\forall s, s' \in S, i \in I. \ Spec(s, i, s') \leftrightarrow \forall \ l \in \mathcal{L}.

(l \neq LocOut(i) \rightarrow s(l) = s'(l)) \land

(l = LocOut(i) \rightarrow s'(l) = SpecOut(i, s(LocIn(i))))

```

• Transition T(s, i) = s'

## **Abstract Specification Relation**

```

\forall s, s' \in S, i \in I. \ Spec(s, i, s') \leftrightarrow \forall l \in \mathcal{L}.

(l \neq LocOut(i) \rightarrow s(l) = s'(l)) \land

(l = LocOut(i) \rightarrow s'(l) = SpecOut(i, s(LocIn(i))))

```

• Transition T(s, i) = s' according to  $Spec \subseteq S \times I \times S$  iff:

## **Abstract Specification Relation**

```

\forall s, s' \in S, i \in I. \ Spec(s, i, s') \leftrightarrow \forall \ l \in \mathcal{L}.

(l \neq LocOut(i) \rightarrow s(l) = s'(l)) \land

(l = LocOut(i) \rightarrow s'(l) = SpecOut(i, s(LocIn(i))))

```

- Transition T(s, i) = s' according to  $Spec \subseteq S \times I \times S$  iff:

- 1. all non-output locations unchanged, and

## **Abstract Specification Relation**

```

\forall s, s' \in S, i \in I. \ Spec(s, i, s') \leftrightarrow \forall \ l \in \mathcal{L}.

(l \neq LocOut(i) \rightarrow s(l) = s'(l)) \land

(l = LocOut(i) \rightarrow s'(l) = SpecOut(i, s(LocIn(i))))

```

- Transition T(s, i) = s' according to  $Spec \subseteq S \times I \times S$  iff:

- 1. all non-output locations unchanged, and

- 2. correct output produced for given input values.

- Output specification:  $SpecOut: I \times V^2 \rightarrow V$ .

## **Abstract Specification Relation**

```

\forall s, s' \in S, i \in I. \ Spec(s, i, s') \leftrightarrow \forall \ l \in \mathcal{L}.

(l \neq LocOut(i) \rightarrow s(l) = s'(l)) \land

(l = LocOut(i) \rightarrow s'(l) = SpecOut(i, s(LocIn(i))))

```

- Transition T(s, i) = s' according to  $Spec \subseteq S \times I \times S$  iff:

- 1. all non-output locations unchanged, and

- 2. correct output produced for given input values.

- Output specification: SpecOut:  $I \times V^2 \rightarrow V$ .

- Abstract spec needed only for theory, not practice.

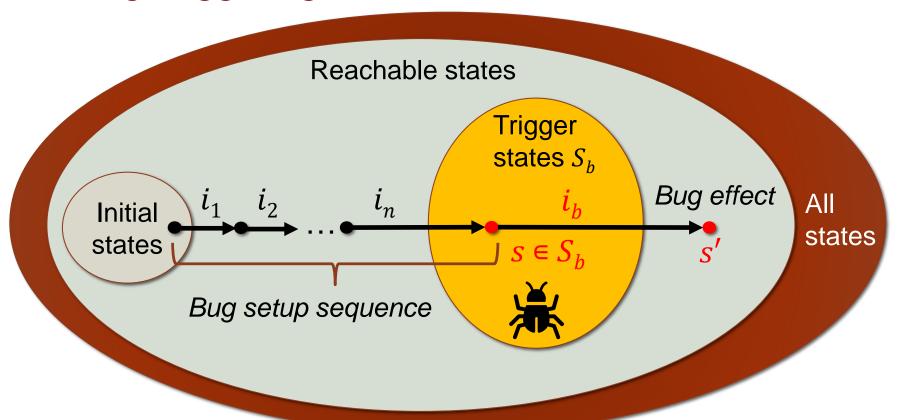

## **Bugs and Processor Correctness**

#### Processor P is correct wrt. Spec:

- $\forall s \in S, i \in I. reach(s) \rightarrow Spec(s, i, T(s, i)).$

- All instructions execute correctly in all reachable states.

#### Bug:

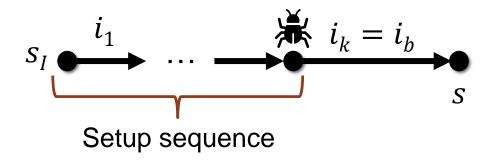

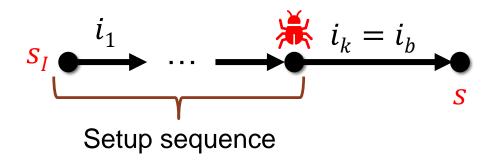

- Instruction  $i_b$  and set  $S_b \subseteq S$  of bug-triggering states.

- $S_b = \{ s \in S \mid reach(s) \land \sim Spec(s, i_b, T(s, i_b)) \}$

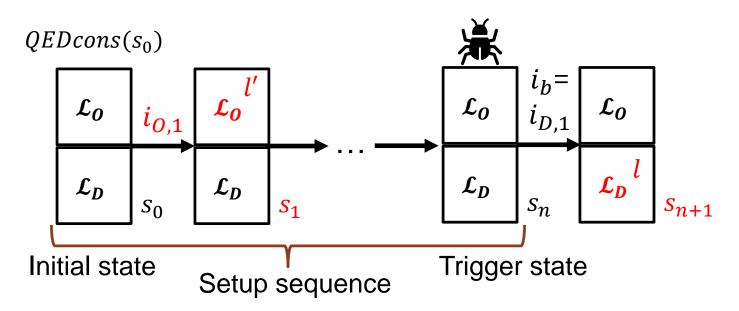

## **Bug Triggering**

## Single-Instruction Bugs and Correctness

Processor P is single-instruction (SI) correct wrt. Spec:

- $\forall s \in Init, i \in I. Spec(s, i, T(s, i)).$

- All instructions execute correctly in all initial states Init.

## Single-Instruction Bugs and Correctness

Processor P is single-instruction (SI) correct wrt. Spec:

- $\forall s \in Init, i \in I. Spec(s, i, T(s, i)).$

- All instructions execute correctly in all initial states Init.

#### Single-instruction (SI) bug:

- $\exists s \in Init, i \in I. \sim Spec(s, i, T(s, i)).$

- No setup sequence, well-studied approaches to checking.

## Single-Instruction Bugs and Correctness

Processor P is single-instruction (SI) correct wrt. Spec:

- $\forall s \in Init, i \in I. Spec(s, i, T(s, i)).$

- All instructions execute correctly in all initial states *Init*.

Single-instruction (SI) bug:

- $\exists s \in Init, i \in I. \sim Spec(s, i, T(s, i)).$

- No setup sequence, well-studied approaches to checking.

Assumption: P is SI-correct.

#### Soundness of SQED

#### Soundness of SQED

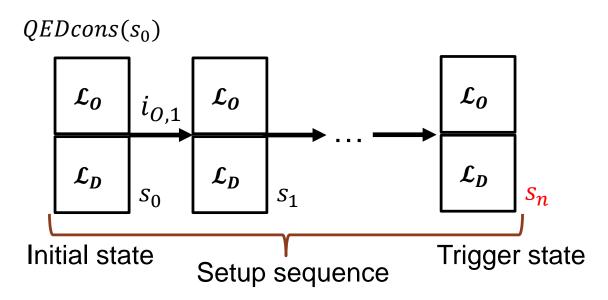

Initial state

- Flexibility in choosing  $L_D$ .

- QED-consistent initial state  $s_0$ .

$\mathcal{L}_{o}$   $\mathcal{L}_{o}$   $\mathcal{L}_{o}$   $\mathcal{L}_{o}$   $\mathcal{L}_{o}$   $\mathcal{L}_{o}$   $\mathcal{L}_{o}$   $\mathcal{L}_{o}$   $\mathcal{L}_{o}$   $\mathcal{L}_{o}$

Initial state

QED test  $\mathbf{i} = (\mathbf{i}_{0,1}, \dots, \mathbf{i}_{0,n}) :: (\mathbf{i}_{D,1}, \dots, \mathbf{i}_{D,n})$  for some  $L_D$ .

- QED-consistent initial state  $s_0$ .

- Let  $i_b = Dup(i_{0,1})$ :  $i_{0,1}$  meets Spec due to SI-correctness.

QED test  $i = (i_{0,1}, ..., i_{0,n}) :: (i_{D,1}, ..., i_{D,n})$  for some  $L_D$ .

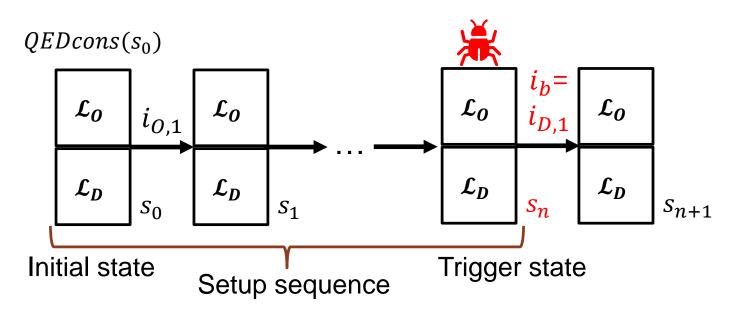

• Setup sequence  $i_{0,1}, \dots, i_{0,n}$  to reach triggering state  $s_n \in S_b$ .

- Setup sequence  $i_{0,1}, \dots, i_{0,n}$  to reach triggering state  $s_n \in S_b$ .

- Bug instruction  $i_b = Dup(i_{0,1})$  fails in  $s_n$ .

- E.g. wrong value at output location l of  $i_b$  in  $s_{n+1}$ .

- Correct value at original output location l' of  $i_{0,1}$  in  $s_1$ .

- Mismatching values at locations l and l' in  $s_{2n}$ .

- Final state  $s_{2n}$  QED-inconsistent.

## Conditional Completeness

Theorem: if a bug-specific QED test i exists, then i fails.

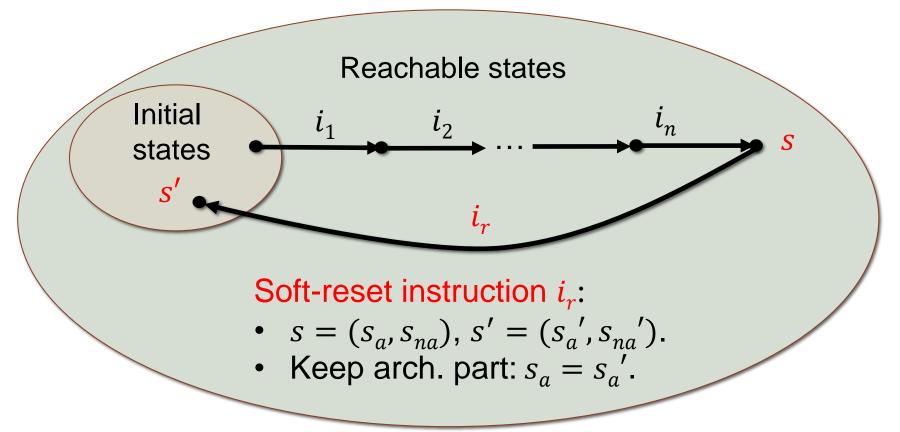

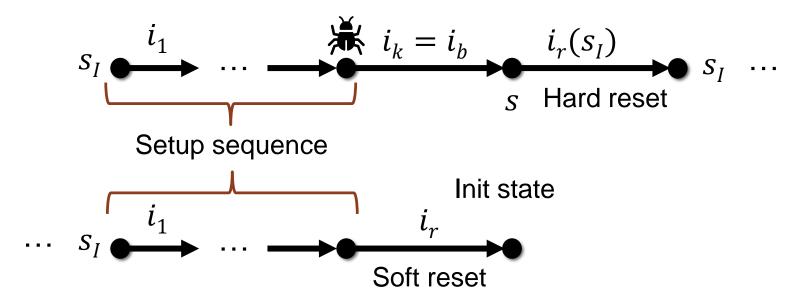

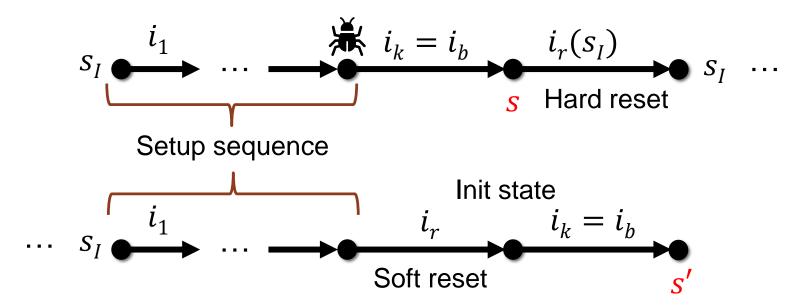

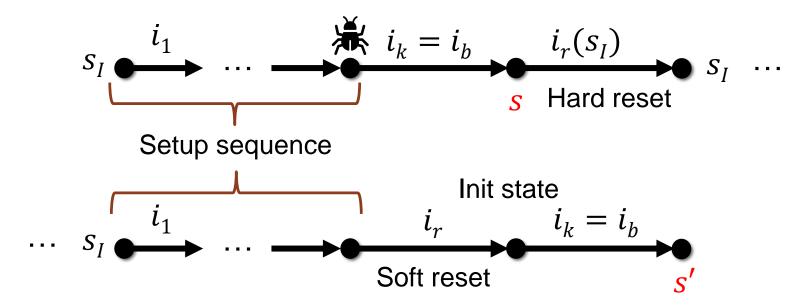

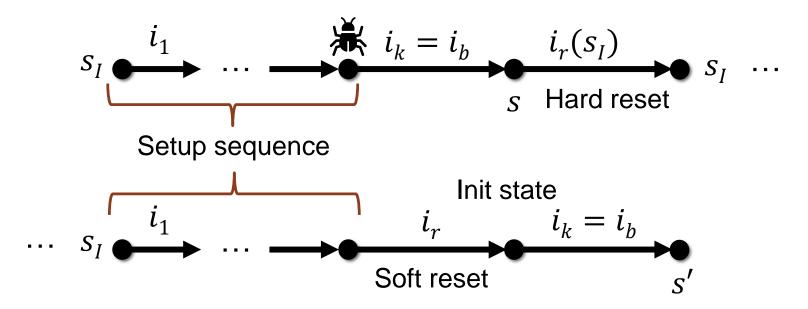

#### **Extensions: Reset Instructions**

#### **Extensions: Reset Instructions**

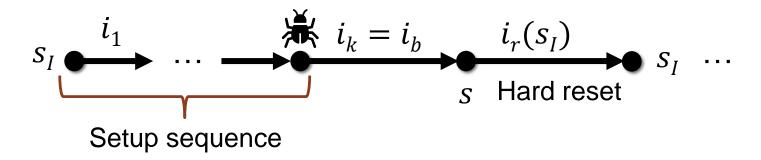

- Bug set up and triggered by  $i_1, \dots, i_k = i_h$ .

- No duplication: check states after  $i_k = i_b$  with(out) reset.

- Bug set up and triggered by  $i_1, ..., i_k = i_h$ .

- Execute  $i_1, ..., i_k = i_b$  from  $s_l \in Init$ : wrong value in state s.

- Execute hard reset in state s, get back to  $s_I$ .

- Idea: execute  $i_1, \dots, i_k = i_b$  again with soft reset before  $i_b$ .

- Execute soft reset in bug-triggering state before  $i_k = i_b$ .

- Make use of SI correctness.

- Bug instruction  $i_k = i_b$  executes correctly.

- Compare s and final state s'.

• QED test with reset fails iff  $s(l) \neq s'(l)$  for a location l.

**Theorem (full completeness):** *if P is SI correct and has no failing QED test with reset, then P is correct.*

## Summary: SQED Soundness and Completeness

Does  $P \in Spec$  hold in M?  $\approx$  Is M self-consistent?

- If M not self-consistent then B ∈ M.

- Self-consistency covers bug B.

No spurious cex

## Summary: SQED Soundness and Completeness

Does  $P \in Spec$  hold in M?  $\approx$  Is M self-consistent?

- If B ∈ M then M not self-consistent.

- Self-consistency covers bug B.

Conditional/full Completeness

#### **Future Work**

#### Leveraging QED test extensions:

- Soft/hard reset not yet applied in practice.

- Design-for-verification approach.

#### Formal model refinements:

- Instruction pipelines, multiprocessor systems.

- Deadlock detection.

- Symbolic starting states.

# Thank you for your attention!